Content Menu

● Understanding the Complexity of PCB Routing

>> The Importance of Proper PCB Routing

● Challenges in Routing PCB with Adjacent SMT Pins

>> Limited Space and High Density

>> Impedance Control

>> Signal Integrity Issues

>> Thermal Considerations

>> Manufacturing Constraints

● Strategies for Effective PCB Routing with Adjacent SMT Pins

>> Optimal Component Placement

>> Layer Stack-up Planning

>> Differential Pair Routing Techniques

>> Via Management

>> Use of Advanced Routing Algorithms

● Best Practices for PCB Routing with Adjacent SMT Pins

>> Maintain Proper Clearances

>> Avoid Routing Between Differential Pairs

>> Implement Length Matching

>> Use of Ground Planes

>> Consider Signal Return Paths

● Advanced Techniques for Challenging Routing Scenarios

>> Microvia Technology

>> Buried and Blind Vias

>> Trace Necking

>> Teardrop Pads

● Emerging Technologies and Future Trends

>> 3D Printed Electronics

>> Artificial Intelligence in PCB Design

>> High-Density Interconnect (HDI) Technology

● Conclusion

● FAQ

>> 1. What is the minimum recommended clearance between PCB traces and SMT pads?

>> 2. How does differential pair routing differ from single-ended routing when dealing with adjacent SMT pins?

>> 3. What are some strategies for improving signal integrity when routing between adjacent SMT pins?

>> 4. How can PCB designers address thermal management issues when routing traces between adjacent SMT pins?

>> 5. What role does PCB layer stack-up play in routing between adjacent SMT pins?

● Citations:

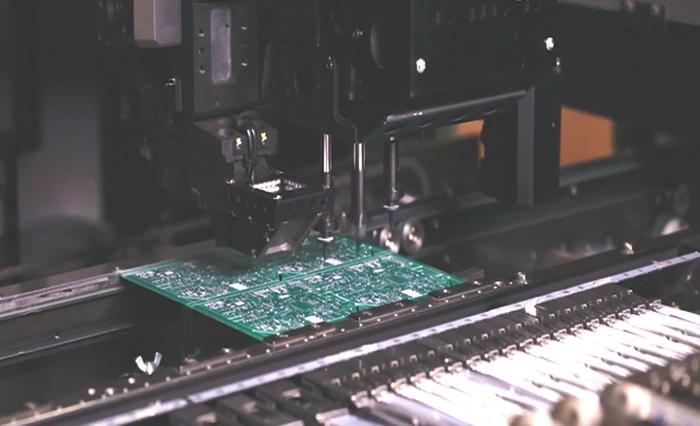

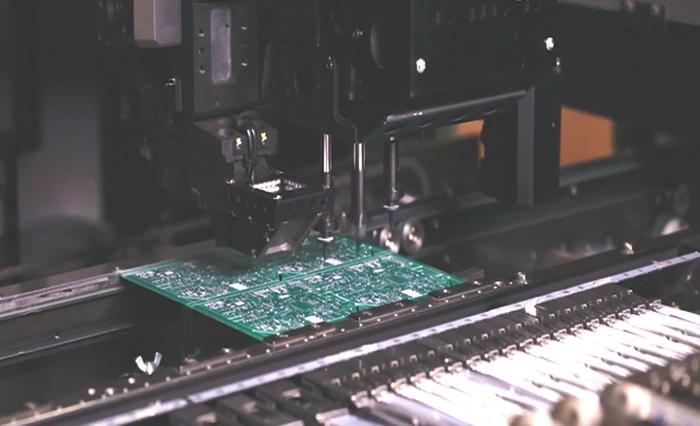

Printed Circuit Board (PCB) design is a critical aspect of electronic product development, and one of the most challenging tasks in this process is routing traces between adjacent Surface Mount Technology (SMT) pins. As electronic devices become increasingly compact and complex, PCB designers face numerous obstacles when attempting to create efficient and reliable connections between components. This article will explore the various challenges associated with routing PCB traces between adjacent SMT pins and discuss strategies to overcome these issues.

Understanding the Complexity of PCB Routing

PCB routing is the process of creating conductive pathways, or traces, between electronic components on a circuit board. When dealing with adjacent SMT pins, designers must navigate a complex landscape of electrical and physical constraints to ensure optimal performance and manufacturability.

The Importance of Proper PCB Routing

Proper PCB routing is crucial for several reasons:

1. Signal Integrity: Well-designed routes minimize signal distortion and interference, ensuring accurate data transmission[1].

2. EMC Compliance: Effective routing helps reduce electromagnetic interference and improve overall electromagnetic compatibility[1].

3. Thermal Management: Proper trace layout can aid in heat dissipation, preventing component overheating[1].

4. Manufacturability: Efficient routing simplifies the manufacturing process and reduces production costs[1].

Challenges in Routing PCB with Adjacent SMT Pins

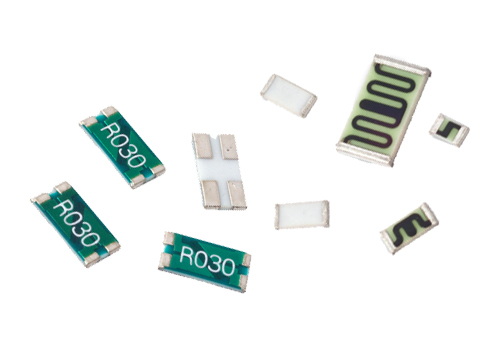

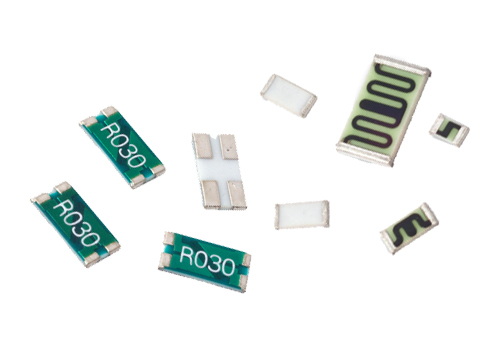

Limited Space and High Density

One of the primary challenges in routing PCB traces between adjacent SMT pins is the limited space available. As component density increases, the gap between pins becomes narrower, making it difficult to route traces without causing short circuits or violating design rules[5].

Impedance Control

Maintaining consistent impedance throughout the trace length is crucial for high-speed signals. When routing between adjacent SMT pins, designers must carefully consider trace width, spacing, and layer transitions to ensure proper impedance control[6].

Signal Integrity Issues

Routing traces in close proximity to each other can lead to signal integrity problems such as crosstalk, reflections, and electromagnetic interference. These issues can cause signal distortion and degrade overall circuit performance[4].

Thermal Considerations

Improper routing can lead to thermal hotspots, especially when dealing with high-power components. Designers must consider thermal management when routing traces between adjacent SMT pins to prevent overheating and potential component failure[1].

Manufacturing Constraints

PCB routing must adhere to manufacturing constraints such as minimum trace width, spacing, and via size. These limitations can be particularly challenging when working with tightly spaced SMT pins[9].

Strategies for Effective PCB Routing with Adjacent SMT Pins

Optimal Component Placement

Proper component placement is crucial for successful PCB routing. Positioning components in a way that minimizes crossing traces and maximizes available space can significantly simplify the routing process[7].

Layer Stack-up Planning

Carefully planning the PCB layer stack-up can provide more routing options and improve signal integrity. Using multiple layers with proper ground and power planes can help isolate signals and reduce interference[6].

Differential Pair Routing Techniques

For high-speed signals, differential pair routing is often employed. When routing differential pairs between adjacent SMT pins, maintaining symmetry and consistent spacing is crucial for signal integrity[3].

Via Management

Strategic placement of vias can help navigate routing challenges in dense areas. However, designers must be cautious of via stub effects and impedance discontinuities when transitioning between layers[6].

Use of Advanced Routing Algorithms

Modern PCB design software often includes advanced routing algorithms that can help optimize trace paths and minimize conflicts between adjacent pins[3].

Best Practices for PCB Routing with Adjacent SMT Pins

Maintain Proper Clearances

Ensure adequate clearance between traces and pads to prevent short circuits and improve manufacturability. The general rule is to maintain a minimum clearance of 5 mils (0.127 mm) between traces and pads[5].

Avoid Routing Between Differential Pairs

When dealing with high-speed differential pairs, avoid routing other traces between the pair to maintain signal integrity. This practice helps prevent crosstalk and maintains the balanced nature of differential signaling[1].

Implement Length Matching

For high-speed interfaces, implement length matching to ensure signals arrive at their destination simultaneously. This is particularly important for parallel buses and differential pairs[1].

Use of Ground Planes

Incorporate ground planes in your PCB design to provide a low-impedance return path for signals and reduce electromagnetic interference[6].

Consider Signal Return Paths

When routing traces, always consider the return path for the signal. Ensuring a clear and unobstructed return path helps maintain signal integrity and reduces EMI issues[6].

Advanced Techniques for Challenging Routing Scenarios

Microvia Technology

For extremely dense designs, consider using microvia technology. Microvias allow for smaller hole sizes and tighter spacing, enabling more routing options in confined spaces[8].

Buried and Blind Vias

Utilizing buried and blind vias can provide additional routing flexibility, especially in multi-layer PCBs. These specialized vias can help reduce congestion on outer layers and improve signal integrity[8].

Trace Necking

In some cases, temporarily reducing trace width (trace necking) can help navigate tight spaces between adjacent SMT pins. However, this technique should be used judiciously to avoid affecting signal integrity[5].

Teardrop Pads

Implementing teardrop pads can improve the mechanical strength of connections between traces and pads, reducing the risk of trace separation during manufacturing or thermal cycling[9].

Emerging Technologies and Future Trends

3D Printed Electronics

Advancements in 3D printing technology are opening new possibilities for PCB design and manufacturing. 3D printed electronics could potentially allow for more complex routing solutions and custom-shaped PCBs[10].

Artificial Intelligence in PCB Design

AI-powered PCB design tools are emerging, offering the potential to automate and optimize complex routing tasks, potentially revolutionizing the way designers approach challenges with adjacent SMT pins[10].

High-Density Interconnect (HDI) Technology

HDI technology continues to evolve, enabling even higher component densities and more complex routing solutions. This technology will likely play a crucial role in addressing future routing challenges[8].

Conclusion

Routing PCB traces between adjacent SMT pins presents numerous challenges for designers, including limited space, signal integrity concerns, and manufacturing constraints. However, by employing best practices, leveraging advanced techniques, and staying abreast of emerging technologies, PCB designers can successfully navigate these challenges and create efficient, reliable, and high-performance circuit boards.

As electronic devices continue to shrink in size while increasing in complexity, the ability to effectively route PCBs with adjacent SMT pins will remain a critical skill for designers. By understanding the challenges and implementing appropriate solutions, designers can ensure that their PCBs meet the demanding requirements of modern electronic systems.

FAQ

1. What is the minimum recommended clearance between PCB traces and SMT pads?

The general rule of thumb is to maintain a minimum clearance of 5 mils (0.127 mm) between traces and SMT pads. However, this can vary depending on the specific design requirements and manufacturing capabilities[5].

2. How does differential pair routing differ from single-ended routing when dealing with adjacent SMT pins?

Differential pair routing requires maintaining consistent spacing and length matching between the two traces of the pair. When routing between adjacent SMT pins, it's crucial to keep the differential pair together and avoid routing other signals between them to maintain signal integrity[3].

3. What are some strategies for improving signal integrity when routing between adjacent SMT pins?

Some strategies include using ground planes, implementing proper impedance control, minimizing via transitions, and employing length matching techniques. Additionally, considering the signal return path and avoiding routing between differential pairs can help maintain signal integrity[1][6].

4. How can PCB designers address thermal management issues when routing traces between adjacent SMT pins?

Designers can address thermal management by considering component placement to allow for proper heat dissipation, using thermal vias to conduct heat away from components, and ensuring adequate copper pour areas for heat spreading. Additionally, avoiding routing high-current traces in densely packed areas can help prevent thermal hotspots[1].

5. What role does PCB layer stack-up play in routing between adjacent SMT pins?

PCB layer stack-up is crucial for effective routing between adjacent SMT pins. A well-designed stack-up can provide more routing options, improve signal integrity, and help with impedance control. Using multiple layers with proper ground and power planes can help isolate signals and reduce interference, making it easier to route traces in tight spaces[6].

Citations:

[1] https://www.protoexpress.com/blog/best-high-speed-pcb-routing-practices/

[2] https://electronics.stackexchange.com/questions/590727/pcb-routing-isolate-through-hole-pins-to-force-routing-through-decoupling-capac

[3] https://core.ac.uk/download/pdf/144446551.pdf

[4] https://electronics.stackexchange.com/questions/408829/electrical-isolation-problems-when-routing-between-pads-of-smt-resistors-caps

[5] https://www.rowsum.com/31-pcb-routing-tips/

[6] https://www.ti.com/lit/an/spraar7j/spraar7j.pdf?ts=1712623000483

[7] https://forum.kicad.info/t/tips-for-relative-small-board-routing/56234

[8] https://www.ti.com/lit/pdf/spraar7

[9] https://patents.google.com/patent/WO2016070545A1/zh

[10] https://www.sierraassembly.com/blog/what-is-pcb-routing-and-how-it-improves-signal-integrity/